QUE

ES MEMORIA

Es un componente indispensable de toda

computadora es su memoria, sin embargo no podría haber computadoras como las

que conocemos

La memoria sirve para almacenar las

instrucciones que se van a ejecutar y también los datos. Los componentes básicos

que lo conforma son los siguientes:

LATCHES

Para crear una memoria de un bit necesitamos

un circuito que de alguna manera

recuerde los valores de entrada anteriores. Podemos construir un sistema

así a partir de dos compuertas NOR

FLIP-FLOPS

En muchos circuitos es necesario muestrear el

valor que hay en una línea dada en un instante dado y almacenado. En esta

variante llamada flip-flop, la transición de estado no ocurre cuando el reloj

es 1, sino durante la transición del reloj de 0 a 1 o de 1 a 0, así la longitud

del pulso de reloj no importa en tanto la transición sea rápida

ORGANIZACIÓN

DE LA MEMORIA

Una organización de la memoria muy utilizada

que satisface este criterio se muestra en la figura,este ejemplo ilustra una

memoria con cuatro palabras de 3 bits.Cada operación lee o escribe una palabra

de 3 bits completa. Si bien la capacidad total de memoria de 12 bits apenas

rebasa la de nuestro flip flop octal, este diseño requiere menos terminales y

loque es mas importante es fácil extenderla a memorias grandes

Aunque la memoria de la figura parece

complicado en si esmuy sencillo,este circuito tiene ocho líneas de entrada y

tres líneas de salida,en principio esta

memoria podría colocarse en un paquete de 14 terminales, incluida la de

potencia y la de tierra en comparación con 20 terminales para el flip flop

octal

CHIPS

DE MEMORIA

Puesto que la tecnología de circuitos

integrados se presta a fabricar chips cuya estructura interna sea un patrón

bidimensional repetitivo, los chips de memoria son una aplicación ideal de esa

tecnología, al mejorar la tecnología el numero de bits que se pueden colocar un

chip aumenta continuamente, duplicándose por lo regular cada 18 meses(ley de

moore).Los chips mas grandes no siempre hacen que los mas pequeños se vuelvan

obsoletos, debido a las diferentes características de capacidad, rapidez,

potencia, precio y facilidad de conexión

Puesto que una computadora normalmente tiene

muchos chips de memoria, se requiere una señal para seleccionar el chip que se

necesita en ese momento, de modo que responda y los demás no lo hagan, se

incluye la señas CS para este fin, la señal se habilita para activar el chip,

la señal WE sirve para indicar que se van a escribir datos, no a leerse. Por

ultimo la señal OE se habilita para alimentar las señales de salida, si no esta

habilitada la salida del chip se desconecta del circuito

Los chips de memoria grandes a menudo se

construyen como matrices de n*n que se direccionan por renglón y columna. Esta

organización reduce el numero de terminales requeridas pero también hace mas

lento el direccionamiento del chip, ya que se necesitan dos ciclos de

direccionamiento uno para el reglón y otro para la columna

LAS

MEMORIAS RAM Y LAS ROM

Una RAM estática se construye internamente

empleando circuitos similares a los flip-flop D básico, tienen la propiedad de

que su contenido se conserva en tanto se sigue alimentando el circuito, las RAM

estáticas son muy rápidas

Una RAM dinámica no usa flip-flops. Una RAM

dinámica es una matriz de celdas, cada una de las cuales contienen un

transmisor y un diminuto condensador, los condensadores pueden cargarse o

descargarse lo que permite almacenar ceros y unos

Las ROM son mucho mas económicos que las RAM

cuando se producen en grandes cantidades, pues así el costo de elaborar la

mascara se diluye, estas memorias son inflexibles porque no pueden modificarse

después de su fabricación y el tiempo que tarde en surtirse un pedido de ROM

puede ser de semanas

Una PROM es parecida a la ROM excepto que

puede programarse en el campo, lo que elimina el retrase por surtido, muchos

PROM contienen una matriz de diminutos fusibles. Un fusible específico puede

quemarse seleccionando su renglón y columna y aplicando después de un voltaje

alto a una terminal especial del chip

La siguiente fue la EPROM que no solo puede

programarse sino también borrarse en el campo, las eprom suelen tener la misma

organización que las RAM estáticas, aun mejor que la EPROM es La EEPROM que

puede borrarse por aplicación de pulsadores, sin tener que colocarse un una

cámara especial para exponerla a luz ultravioleta

REFERENCIAS

BIBLIOGRAFICAS

Andrew S. Tanenbaum (2000),

Organización de Computadoras un enfoque estructurado, Estado de México

John L. Hennessy y David A.

Patterson (1993), Arquitectura de Computadoras un enfoque cuantitativo, Mcgraw-Hillpnteramericana

De España

JERARQUIA

DE MEMORIA

INTRODUCCIÓN

La solución para almacenar una gran cantidad de datos es

el uso de la jerarquía de memoria

DESARROLLO

En la jerarquía de memoria se reconoce los siguientes

niveles:

En la cúspide esta los registros de la CPU a los que

puede tenerse acceso a la velocidad máxima del CPU

Memoria cache que actualmente es el orden de 32k a unos

cuantos megabytes

Memoria principal con tamaños que actualmente van de los

16M hasta decenas de gigabytes

Discos magnéticos para el almacenamiento permanente

Cinta magnética y discos ópticos para el almacenamiento

de archivos

Al bajar por la jerarquía 3 parámetros clave crecen:

Primero.- El tiempo de acceso se alarga, los registros de

la CPU se pueden acceder en nanosegundos, la memoria cache requiere un múltiplo

pequeño del tiempo de acceso de los registros, los tiempos de acceso a el disco

magnético es de por lo menos 10ms, y el

acceso a cinta y a óptico se puede medir en segundos.

Segundo.- la capacidad de almacenamiento aumenta al bajar

la jerarquía, los registros tienen por lo menos tienen 128 bytes, los caches a

unos megabytes, las memorias principales decenas o miles de megabytes, los

discos magnéticos de unos a decenas de gigabytes, la cinta y los discos ópticos

se guardan fuera de línea ósea su

límite depende del propietario.

Tercero.- el número de bits que se obtiene por dólar

invertido aumenta al bajar la jerarquía, la memoria principal se mide en

dólares/megabytes, almacenamiento de disco centavos de dólar/megabyte, y la

cinta en dólares/gigabyte

REFERENCIAS BIBLIOGRAFICAS

Andrew S. Tanenbaum (2000), Organización de Computadoras un enfoque estructurado, Estado de México

John L. Hennessy y David A. Patterson (1993), Arquitectura de Computadoras un enfoque cuantitativo, Mcgraw-Hillpnteramericana De España

MEMORIA

PRINCIPAL

INTRODUCCION

La memoria principal satisface las demandas

de as caches y unidades vectoriales y sirve como interfaz de entrada y salida

ya que es el destino de la entrada asi como la fuente para la salida, las

medidas de rendimiento de la memoria principal hacen énfasis a la latencia y al

ancho de banda

DESARROLLO

LATENCIA

EN LA MEMORIA

La latencia de la memoria principal es la

preocupación primordial de la cache

mientras que el ancho de banda de la memoria es la preocupación

primordial de las E/S y unidades vectoriales.

La latencia de memoria tradicionalmente se

expresa usando dos medidas: tiempo de acceso y duración del ciclo

- Ø Tiempo de acceso.-es el tiempo desde que se pide una lectura hasta que llega la palabra deseada

- Ø Duración del ciclo.-es el tiempo mínimo entre peticiones a memoria

ORGANIZACIÓN

PARA MEJORAR EL RENDIMIENTO DE LA MEMORIA PRINCIPAL

Una mejora en el ancho de banda permitiría

incrementar el tamaño de los bloques de cache sin el correspondiente incremento

en la peñalizacion de fallos

El rendimiento de la organización básica de

memoria es:

- Ø 1 ciclo de reloj para enviar la dirección

- Ø 6 ciclos de reloj para el tiempo de acceso por palabra

- Ø 1 ciclo de reloj para enviar una palabra de datos

Dado un bloque de cache de cuatro palabras,

la penalización de fallos es de 32 ciclos de reloj, y un ancho de banda de

medio byte por ciclo de reloj

Opciones para conseguir sistemas de memoria

más rápidos

MEMORIA

PRINCIPAL MÁS ANCHA

Los caches están organizados con una anchura

de una palabra porque la mayoría de los accesos de la CPU son de ese tamaño

A su vez la memoria principal tiene el ancho

de una palabra para que coincida con la anchura de la cache, duplicar o

cuadruplicar el ancho de la memoria es duplicar o cuadruplicar también el ancho

de banda de memoria

El ancho de banda es un byte por ciclo de

reloj, en un ancho de dos palabras y de dos bytes por ciclo de reloj cuando la

memoria tiene un ancho de cuatro palabras

ENTRELAZADO

DE DRAM ESPECIFICO PARA MEJORAR EL RENDIMIENTO DE LA MEMORIA PRINCIPAL

Los tiempos de acceso a las DRAM se dividen

en accesos a filas y accesos a columnas. Las DRAM disponen de un buffer de una

fila de bits dentro de la DRAM para los accesos a las columnas.

Hay tres versiones para esta optimización:

Modo

nibble.-la DRAM puede proporcionar tres bits extra de posiciones

secuenciales para cada acceso a filas

Modo

de pagina.-El buffer actúa como una SRAM, cambiando las

direcciones de las columnas, se puede acceder a bits aleatorios en el buffer

hasta el siguiente acceso a fila o tiempo de refresco

Columna

estática.-Muy similar al modo de página, excepto que no es

necesario acertar la línea de strobe de acceso a columnas cada vez que cambie

la dirección de la columna; esta opción se ha denominado SCRAM, para la DRAM de

columna estática

A partir de DRAM de Mbit,la mayoría de los

dados pueden realizar alguna de las tres opciones, seleccionando la

optimización en el instante que el dado se encapsula al escoger los pads que se

van a usar, estas operaciones cambian la definición del tiempo del ciclo para

las DRAM.

REFERENCIAS BIBLIOGRAFICAS

Andrew S. Tanenbaum (2000), Organización de Computadoras un enfoque estructurado, Estado de México

John L. Hennessy y David A. Patterson (1993), Arquitectura de Computadoras un enfoque cuantitativo, Mcgraw-Hillpnteramericana De España

MEMORIA

CACHE

INTRODUCCION

Cache es el nombre escogido para representar

el nivel de jerarquía de memoria entre la CPU y la memoria principal. El

concepto de cache es mas joven que la arquitectura IBM 360 pero hoy aparecen caches en todo tipo de

computadoras, la palabra cache a sustituido a “BUFFER “en muchos de los

circuitos informáticos

Rango típico de parámetros de la jerarquía de

memoria cache

DESARROLLO

El diseño de las caches cada vez es más

importante para CPU de alto rendimiento

- Ø Uno de los aspectos es el tamaño de la cache, cuanto mas grande es el cache mejor funciona, pero también cuesta mas

- Ø Un segundo aspecto es el tamaño de la línea de cache, un cache de 16KB se puede dividir en 1k líneas de 16 BYTES ,2k líneas de 8 bytes y otras combinaciones

- Ø Un tercer aspecto es la organización del cache es decir como hace el cache para saber que palabra de memoria contiene en un momento dado

- Ø Un cuarto aspecto es el de las instrucciones y los datos se guardaran en el mismo cache o en caches distintos

Un diseño de cache unificado es mas sencillo

y automáticamente equilibra las obtenciones de instrucciones frente a las

obtenciones de datos

En un quinto aspecto es el número de caches,

hoy en día es raro tener chips con un cache primario en el chip de la CPU, un

cache secundario fuera del chip pero en el mismo paquete y un tercer cache

todavía más lejos

ORGANIZACIÓN

DE LA CACHE

Se divide en tres categorías:

- Ø Si cada bloque solo tiene un lugar donde puede aparecer en la cache se dice que es de correspondencia directa

- Ø Si un bloque se puede colocar en cualquier parte de la cache se lo denomina totalmente asociativa

- Ø Si un bloque se puede colocar en un conjunto restringido de la cache se lo dice que es asociativa por conjuntos

La cache tiene una etiqueta de dirección en

cada bloque que identifica la dirección dela estructura del bloque. La etiqueta

de cada bloque se lo va verificando para ver si coincide con la dirección de

estructura requerida por la CPU

Para verificar que un bloque de cache no

tiene información valida, el procedimiento es añadir un bit de validez a la etiqueta para que este

indique si esta entrada contiene o no una dirección valida

La etiqueta se lo utiliza para comprobar

todos los bloques del conjunto el índice se utiliza para seleccionar el

conjunto y el desplazamiento es la dirección del dato deseado

RENDIMIENTO

DE LA CACHE

El tiempo de la CPU se puede dividir en

ciclos de reloj que la CPU maneja en la

ejecución de del programa y en los ciclos de reloj que la CPU emplea esperando

al sistema de memoria

Tiempo de CPU= (ciclos de reloj de ejecución

CPU + ciclos de reloj de detención –memoria).duración de ciclo de reloj

La formula anterior plantea la siguiente

pregunta de si los ciclos de reloj para un acceso a cache se debe considerar el

reloj de detención de memoria o el de ejecución de CPU. Ambos se los puede usar

pero el mas correcto es el uso de los ciclos de reloj de ejecución de CPU

Entonces los ciclos de reloj de detención de

memoria se pueden definir como la función del número de accesos a memoria por

programa.

Ciclos de reloj de detención de

memoria=(acceso a memoria/programa)*frecuencia de fallos*penalización de fallos

FORMULA

DE TIEMPO – CPU

Tiempo de CPU=IC+ (CPI+ (Accesos a

memoria/instrucciones)*Frecuencia de fallos*Penalización de fallos)*Tiempo de

ciclo de reloj

REFERENCIAS BIBLIOGRAFICAS

Andrew S. Tanenbaum (2000), Organización de Computadoras un enfoque estructurado, Estado de México

John L. Hennessy y David A. Patterson (1993), Arquitectura de Computadoras un enfoque cuantitativo, Mcgraw-Hillpnteramericana De España

MEMORIA

VIRTUAL

INTRODUCCION

En cualquier instante de tiempo los

computadores están corriendo múltiples procesos, cada uno con su propio espacio

de direcciones, seria muy caro dedicar una memoria de tamaño igual al espacio

total de direcciones a cada proceso, especialmente dado que muchos procesos

utilizan solo una pequeña parte de su espacio de direcciones, una manera de

hacer esto es la memoria virtual, divide la memoria física en bloques y los

asigna a diferentes procesos.

DESARROLLO

La memoria virtual es esencial para las

computadoras actuales, la compartición no es la razón por la cual se invento la

memoria virtual. Si antes un programa era demasiado grande para la memoria

física incumbía al programador ajustarlo.

La memoria virtual, inventada para aligerar a

los programadores de este peso, gestionaba automáticamente los dos niveles de

jerarquía de memoria representada por la memoria principal y la secundaria.

La memoria virtual igual simplifica la carga

del programa para su ejecución. Denominado reubicación este procedimiento permite

que el mismo programa se ejecute en cualquier posición de la memoria física.

Con la memoria virtual la CPU produce direcciones virtuales que son

traducidas por una combinación de Harvard y software a direcciones físicas, que

pueden ser utilizadas para acceder a la memoria principal. Este proceso se

denomina correspondencia de memoria o traducción de direcciones.

La memoria virtual controla dos niveles de la

jerarquía de la memoria que son la DRAM y los discos magnéticos.

RANGOS

TIPICOS DE ÀRAMETROS PARA MEMORIA VIRTUAL

Los sistemas de memoria virtual se pueden

categorizar en dos clases: los de bloques de tamaño fijo, denominados páginas y

los de bloques de tamaño variable denominados segmentos. Las paginas

normalmente tienen un tamaño fijo entre 512 y

192 bytes, mientras que el tamaño del segmento es variable.

La decisión de utilizar memoria virtual

paginada frente a la segmentada afecta a la CPU. Él direccionamiento paginado

tiene una única dirección de tamaño fijo dividida en numero de pagina y

desplazamiento en una pagina, análogo al direccionamiento de la cache

REFERENCIAS BIBLIOGRAFICAS

Andrew S. Tanenbaum (2000), Organización de Computadoras un enfoque estructurado, Estado de México

John L. Hennessy y David A. Patterson (1993), Arquitectura de Computadoras un enfoque cuantitativo, Mcgraw-Hillpnteramericana De España

MEMORIAS

SECUNDARIAS

INTRODUCCION

Por más grande que sea la memoria principal,

siempre es demasiado pequeña. La gente siempre quiere almacenar mas información

de la que cabe en la memoria, primordialmente porque a medida que la tecnología

mejora se va queriendo guardar mas y mas información.

La solución tradicional para almacenar una

gran cantidad de datos es una jerarquía de memoria

En la cúspide de esta pirámide están los

registros de la CPU, luego viene la memoria cache que actualmente es del orden de

32KB a unos cuantos megabytes, sigue la memoria principal con tamaños que

actualmente van de 16Mb para los sistemas mas económicos hasta decenas de

gigabytes, luego se encuentran los discos magnéticos y por ultimo tenemos la

cinta magnética y los discos ópticos para el almacenamiento de archivos

DISCOS

MAGNETICOS

Un disco magnético consiste en uno o más

platos de aluminio con un recubrimiento magnetizable. Originalmente estos

platos llegaron a tener 50 cm de diámetro, pero en la actualidad suelen ser de 3

a 12 cm, y algunos discos para computadoras portátiles tienen diámetros de menos

de 3cm y se siguen encogiendo. Una cabeza de disco contiene una bobina de

inducción flota sobre la superficie y muy cerca de ella, descansando en un

colchón de aire. Cuando una corriente positiva o negativa pasa por la cabeza,

magnetiza la superficie justo debajo de ella, alineando las partículas

magnéticas hacia la izquierda o hacia la derecha, dependiendo de la polaridad

de la corriente de la unidad.

DISCOS

FLEXIBLES

Con la llegada de la computadora personal se

requiero una forma de distribuir software, la solución fue el disquete o disco

flexible, un medio pequeño y removible que recibió ese nombre ya que los

primeros eran físicamente flexibles.

Las características generales son las mismas

que las de los discos que acabamos de describir, excepto que, a diferencia de

los discos duros, en los que las cabezas flotan sobre la superficie en un

colchón de aire en rápido movimiento, las cabezas de las unidades de disco si

tocan los disquetes, el resultado es que tanto los medios como las cabezas se

desgastan con comparativa rapidez, a fin de reducir el desgaste las

computadoras personales retraen las cabezas y detienen la rotación cuando una

unidad no esta leyendo o escribiendo, por esta razón cuando se emite el orden

de leer o escribir hay un retraso de medio segundo.

DISCOS

IDE

Los discos IDE y EIDE eran originalmente solo

para sistemas basados en Intel, ya que la interfaz es una copia exacta del bus

de la IBM PC, sin embargo hoy día unas cuantas computadoras mas los usan por su

bajo precio

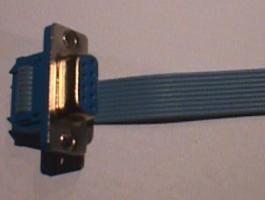

DISCOS

SCSI

Los discos SCSI no son diferentes de los IDE

en cuanto a la organización de sus cilindros, pistas y sectores, pero tienen

una interfaz diferente y tasas de transferencia mucho mas altas.

Puesto que los discos SCSI tienen una tasa de

transferencia alta, son el disco estándar en casi todas las estaciones de

trabajo, también son el disco estándar de las MACINTOSH y son comunes en las PC

Intel actuales

CD-ROM

Los discos ópticos tienen una densidad de

grabación mayor que los discos magnéticos convencionales. Los discos ópticos en

si se crearon originalmente para grabar programas de televisión, pero se les

puede dar un uso más estético como dispositivos de almacenamiento para

computadora.

Los discos ópticos de primera generación

fueron inventados por el conglomerado de electrónica holandés Philips para

grabar películas. Tenían 30 cm de diámetro y se vendían con el nombre de

LaserVision, pero no se popularizaron fuera de Japón

Los CD-ROM se han vuelto muy populares para

publicar juegos, películas, enciclopedias, atlas y obras de referencia de todo

tipo. Casi todo el software comercial se vende ahora en CD-ROM, su combinación

de alta capacidad y bajo costo de fabricación los hace ideales para un

sinnúmero de aplicaciones

REFERENCIAS BIBLIOGRAFICAS

Andrew S. Tanenbaum (2000), Organización de Computadoras un enfoque estructurado, Estado de México

John L. Hennessy y David A. Patterson (1993), Arquitectura de Computadoras un enfoque cuantitativo, Mcgraw-Hillpnteramericana De España

BUSES

La mayor parte de las computadoras tiene una

estructura como se lo ve en la figura de

abajo

Esta solo tiene un bus que sirve para

conectar la CPU, la memoria y los dispositivos de E/S, casi todos los sistemas

tienen dos o mas buses. Cada dispositivo de E/S consta de dos partes una que

contiene casi todos los circuitos electrónicos, llamado controlador y una que

contiene el dispositivo de E/S como una

unidad de disco

El controlador suele estar contenido en una

tarjeta que se inserta en una ranura desocupada, con excepción de los

controladores que no son opcionales como el del teclado

El controlador se conecta a su dispositivo

con un cable unido a un conector en la parte de trasera del gabinete

La tarea de un controlador es dominar su dispositivo

de E/S y manejar su acceso al bus

El bus ISA eran demasiados lentos por lo que

se creo un bus mucho mas rápido y se esta utilizando en la actualidad que es el

bus PCI Intel diseño este bus pero decidió colocar todas las patentes den el

dominio publico para animar a toda la industria a que lo adoptaron

El bus PCI se puede usar en muchas

configuraciones, el controlador se comunica con la memoria y con el bus PCI

directamente de modo que el trafico entre la CPU y la memoria no usa el bus

PCI, en cambio los que necesitan un gran ancho de banda como los discos SCSI se

pueden conectar directamente al bus PCI, además el bus PCI tiene un puente con

el bus ISA lo que permite seguir usando controladores ISA y sus dispositivos

REFERENCIAS BIBLIOGRAFICAS

Andrew S. Tanenbaum (2000), Organización de Computadoras un enfoque estructurado, Estado de México

John L. Hennessy y David A. Patterson (1993), Arquitectura de Computadoras un enfoque cuantitativo, Mcgraw-Hillpnteramericana De España

TIPOS

DE BUSES

Existen dos grandes tipos clasificados por el

método de envío de la información: bus paralelo o bus serie.

Hay diferencias en el desempeño y hasta hace

unos años se consideraba que el uso apropiado dependía de la longitud física de

la conexión: para cortas distancias el bus paralelo, para largas el serial.

BUS

PARALELO

Es un bus en el cual los datos son enviados

por bytes al mismo tiempo, con la ayuda de varias líneas que tienen funciones

fijas. La cantidad de datos enviada es bastante grande con una frecuencia

moderada y es igual al ancho de los datos por la frecuencia de funcionamiento.

En los computadores ha sido usado de manera intensiva, desde el bus del

procesador, los buses de discos duros, tarjetas de expansión y de vídeo, hasta las

impresoras.

El front-side bus de los procesadores Intel

es un bus de este tipo y como cualquier bus presenta unas funciones en líneas

dedicadas:

Las líneas de dirección son las encargadas de

indicar la posición de memoria o el dispositivo con el que se desea establecer

comunicación.

Las líneas de control son las encargadas de

enviar señales de arbitraje entre los dispositivos. Entre las más importantes

están las líneas de interrupción, DMA y los indicadores de estado.

Las líneas de datos transmiten los bits de

forma aleatoria de manera que por lo general un bus tiene un ancho que es

potencia de 2.

Un bus paralelo tiene conexiones físicas

complejas, pero la lógica es sencilla, que lo hace útil en sistemas con poco

poder de cómputo. En los primeros microcomputadores, el bus era simplemente la

extensión del bus del procesador y los demás integrados "escuchan"

las línea de direcciones, en espera de recibir instrucciones. En el PC IBM

original, el diseño del bus fue determinante a la hora de elegir un procesador

con I/O de 8 bits (Intel 8088), sobre uno de 16 (el 8086), porque era posible

usar hardware diseñado para otros procesadores, abaratando el producto.

BUS

SERIE

En este los datos son enviados, bit a bit y

se reconstruyen por medio de registros o rutinas de software. Está formado por

pocos conductores y su ancho de banda depende de la frecuencia. Es usado desde

hace menos de 10 años en buses para discos duros, unidades de estado sólido,

tarjetas de expansión y para el bus del procesador.

REFERENCIAS BIBLIOGRAFICAS

Andrew S. Tanenbaum (2000), Organización de Computadoras un enfoque estructurado, Estado de México

John L. Hennessy y David A. Patterson (1993), Arquitectura de Computadoras un enfoque cuantitativo, Mcgraw-Hillpnteramericana De España

UNIDAD

CENTRAL DE PROCESAMIENTO

INTRODUCCION

Es el cerebro de la computadora, su función

principal es de ejecutar programas almacenados en la memoria principal buscando

sus instrucciones y examinándolas para después ejecutarlas una tras otra. Los

componentes están conectados por un bus

para transmitir direcciones datos y señales de control

DESARROLLO

La CPU se compone de varias partes, la unidad

de control se encarga de buscar instrucciones de la memoria principal y

determinar su tipo. La unidad aritmética y lógica realiza operaciones como suma

y AND booleana necesarias para ejecutar las instrucciones

La cpu también contiene una memoria pequeña y

de alta velocidad que sirve para almacenar resultados temporales y cierta

información de control. Esta memoria se compone de varios registros, cada uno

de los cuales tiene cierto tamaño y función. Los registros pueden leerse y

escribirse a alta velocidad porque están dentro de la CPU

El registro mas importante es el contador de

programa que apunta a la siguiente instrucción que debe buscarse para

ejecutarse. Otro registro importante es el registro de instrucciones que

contiene la instrucción que se esta ejecutando. Casi todas las computadoras

tienen varios registros más, algunos de propósito general y otros para fines

específicos

La CPU ejecuta cada instrucción en una serie

de pasos pequeños, los pasos son los siguientes:

- Ø Buscar la siguiente instrucción de la memoria y colocarla en el registro de instrucciones

- Ø Modificar el contador de programa de modo que apunte a la siguiente instrucción

- Ø Determinar el tipo de instrucción que se trajo

- Ø Si la instrucción utiliza una palabra de la memoria determinar donde esta

- Ø Buscar la palabra, si es necesario, y colocarla en un registro de la CPU

- Ø Ejecutar la instrucción

- Ø Volver al paso 1 para comenzar a ejecutar la siguiente instrucción

REFERENCIAS BIBLIOGRAFICAS

Andrew S. Tanenbaum (2000), Organización de Computadoras un enfoque estructurado, Estado de México

John L. Hennessy y David A. Patterson (1993), Arquitectura de Computadoras un enfoque cuantitativo, Mcgraw-Hillpnteramericana De España

UNIDAD

ARITMETICA LOGICA

INTRODUCCION

Todas la computadoras contienen un circuito

para obtener el and, el or y la suma de dos palabras de maquina. Por lo

regular, un circuito de este tipo para palabras de n bits se construye con n

circuitos idénticos para las posiciones de bit individuales.

DESARROLLO

La esquina izquierda de la ALU contiene un

decodificador de 2 bits que genera señales de habilitación para las cuatro

operaciones, con base en las señales de control F0 Y F1. Dependiendo de los

valores de F0 y f1 una y solo una de las cuatros líneas de habilitación se

selecciona

La esquina superior izquierda contiene la

lógica necesaria para calcular A AND B A OR B Y B NEGADO, pero solo uno de

estos resultados pasa a la compuerta or final, dependiendo de las líneas de

habilitación que salen del decodificador

La esquina inferior derecha de la ALU

contiene un sumador completo para calcular la suma de A Y B e incluye manejo de acarreos porque es

probable que se conecten juntos varios de estos circuitos para efectuar

operaciones con palabras enteras

La siguiente figura es una ALU de un bit

conectadas para formar una ALU de ocho bits

REFERENCIAS BIBLIOGRAFICAS

Andrew S. Tanenbaum (2000), Organización de Computadoras un enfoque estructurado, Estado de México

John L. Hennessy y David A. Patterson (1993), Arquitectura de Computadoras un enfoque cuantitativo, Mcgraw-Hillpnteramericana De España

UNIDAD DE CONTROL

INTRODUCCION

La unidad de control (UC) es uno de

los tres bloques funcionales principales en los que se divide una unidad central de procesamiento (CPU).

Los otros dos bloques son la unidad de

proceso y el bus de entrada/salida.

DESARROLLO

Su función es buscar las

instrucciones en la memoria

principal, decodificarlas (interpretación) y ejecutarlas, empleando

para ello la unidad.

Existen dos tipos de unidades

de control, las cableadas, usadas generalmente en máquinas sencillas, y las

microprogramadas, propias de máquinas más complejas. En el primer caso, los

componentes principales son el circuito de lógica secuencial, el de control de estado, el

de lógica combinacional y el de emisión

de reconocimiento de señales de control. En el segundo caso, la

microprogramación de la unidad de control se encuentra almacenada en una

micromemoria, a la cual se accede de manera secuencial para posteriormente ir

ejecutando cada una de las microinstrucciones.

En computadoras, la unidad de

control fue históricamente definida como una parte distinta del modelo de

referencia de 1946 de la Arquitectura de von Neumann. En diseños

modernos de computadores, la unidad de control es típicamente una parte interna

del CPU.

OPERACIÓN GENERAL

Las salidas de la unidad de

control se encargan de controlar la actividad del resto del dispositivo. Se

puede pensar en una unidad de control como una máquina de estado

finito.

La unidad de control es la

circuitería que controla el flujo de datos a través del procesador, y coordina

las actividades de las otras unidades dentro de él. De una manera, es el

"cerebro dentro del cerebro", pues controla lo que sucede dentro del

procesador, que a su vez controla el resto del PC.

Algunos ejemplos de

dispositivos que requieren una unidad de control son los CPUs y los GPUs. La

edad de la información moderna no sería posible sin diseños complejos de la

unidad de control.

FUNCIONES

Las funciones realizadas por

la unidad de control varían grandemente por la arquitectura interna del CPU,

pues la unidad de control realmente implementa esta arquitectura. En un

procesador regular que ejecuta las instrucciones x86 nativamente,

la unidad de control realiza las tareas de leer, decodificar, manejo de la

ejecución y almacenamiento de los resultados. En un procesador x86 con un

núcleo RISC, la unidad de control tiene considerablemente más trabajo que

hacer. Ella maneja la traducción de las instrucciones x86 a las

microinstrucciones del RISC, maneja la planificación de las microinstrucciones

entre las varias unidades de ejecución, y maneja la salida de estas unidades

para cerciorarse de que terminen donde supuestamente deben ir. En uno de estos

procesadores la unidad de control está dividida en otras unidades debido a la

complejidad del trabajo que debe realizar, almacena los datos mas utilizados de

modo que se buscan primero en la computadora y luego en la RAM

REFERENCIAS BIBLIOGRAFICAS

Andrew S. Tanenbaum (2000), Organización de Computadoras un enfoque estructurado, Estado de México

John L. Hennessy y David A. Patterson (1993), Arquitectura de Computadoras un enfoque cuantitativo, Mcgraw-Hillpnteramericana De España

SISTEMAS

DE E/S

INTRODUCCION

En las computadoras personales actuales se

usan tres esquemas de E/S distintos, estos son:

- Ø E/S programada con espera actica

- Ø E/S controlada por interrupciones

- Ø E/S de acceso directo a memoria

DESARROLLO

El método de E/S mas sencillo posible es la

E/S programada, que suele usarse en los microprocesadores de bajo costo,

como los sistemas incorporados o en los sistemas

que deben responder rápidamente a cambios externos estas CPU por lo regular tienen una sola

instrucción de entrada y una sola instrucción de entrada y una sola instrucción

de salida. Cada una de estas instrucciones secciona uno de los dispositivos de

E/S. el procesador debe ejecutar una sucesión explicita de instrucciones para

cada uno de los caracteres leídos o escritos

La principal ventaja de la E/S programada es

que la CPU pasa casi todo su tiempo en un ciclo corto esperando que el

dispositivo este listo. Este enfoque se llama espera activa. Si la CPU no tiene

nada más que hacer la espera actica podría ser lo mejor, pero si hay otras

cosas que hacer como ejecutar otros programas, la espera activa es un

desperdicio de recursos y se necesita un método de E/S distinto

La forma de deshacerse de la espera activa es

hacer que la CPU inicie el dispositivo de E/S y le diga que genere una

interrupción cuando haya terminado

La señal de interrupción se genera obteniendo

el AND del bit HABILITAR INTERRUPCIONES y el bit READY. Si el software habilita

las interrupciones primero ocurrirá una interrupción de inmediato, porque el

bit READY será 1.

Aunque la E/S controlada por interrupciones

es un gran adelanto en comparación a la programada le falta mucho para ser

perfecta, el problema es que se requiere una interrupción por cada carácter transmitido,

y la solución fue un controlador directo a la memoria (DMA, Direct Memory

Access)

REFERENCIAS BIBLIOGRAFICAS

Andrew S. Tanenbaum (2000), Organización de Computadoras un enfoque estructurado, Estado de México

John L. Hennessy y David A. Patterson (1993), Arquitectura de Computadoras un enfoque cuantitativo, Mcgraw-Hillpnteramericana De España

ENTRADA

Y SALIDA DE DMA

El chip DMA contiene cuatro registros, todos

los cuales pueden ser cargados por software que se ejecuta en la CPU.

- El primero contiene la dirección de memoria que se leerá o en la que se escribirá.

- El segundo contiene el número de bytes (o palabras) que se transfieren

- El tercero especifica el número de dispositivo o espacio de direcciones de E/S que se usara, con lo que se especifica que dispositivo de E/S se desea

- El cuarto indica si los datos se escribirán en el dispositivo de E/S o se leerán de el

Para escribir un bloque de 32 bytes de la

dirección de memoria 100 en una terminal la CPU escribe los números 100,32 y 4

en los primeros tres registros de DMA, y luego el código de escribir en el

cuarto

Una vez inicializado con estos valores, el

controlador de DMA emita una solicitud de bus para leer el BYTE 100 de la

memoria, del mismo modo como la CPU leería de la memoria, una vez que obtiene

el byte el controlador de DMA emite una solicitud de E/S al dispositivo 4, para

escribir el byte en el. Una vez completadas ambas operaciones el controlador de

DMA incrementa en uno su registro de dirección y decrementa en 1 su registro de

cuenta

Cuando la cuenta por fin llega a 0, el

controlador de DMA deja de transmitir datos y habilita la línea de interrupción

en el chip de CPU. Con DMA, la CPU solo tiene que inicializar unos cuantos

registros. Algunos controladores de DMA tienen dos o más conjuntos de

registros, lo que les permite controlar varias transferencias simultáneas

Si bien el DMA alivia a la CPU de la gran

carga de E/S, el proceso no es totalmente gratuito, si un dispositivo de alta

velocidad como un disco s esta controlando por DMA se requerirán muchos ciclos

de bus, tanto para las referencias a la memoria como para las referencias al

dispositivo. Durante estos ciclos la CPU tendrá que esperar. El proceso por el

que el controlador de DMA quita ciclos de bus a la CPU se denomina robo de

ciclos

REFERENCIAS BIBLIOGRAFICAS

Andrew S. Tanenbaum (2000), Organización de Computadoras un enfoque estructurado, Estado de México

John L. Hennessy y David A. Patterson (1993), Arquitectura de Computadoras un enfoque cuantitativo, Mcgraw-Hillpnteramericana De España

ENTRADAS

Y SALIDAS MAPEADAS

INTRODUCCION

E/S mapeada en memoria es un

método de implementar entradas/salidas entre los periféricos y la CPU en un

computador.

DESARROLLO

La E/S mapeada en memoria usa el mismo bus de

direcciones para memoria y dispositivos de E/S, y las instrucciones de la CPU

usadas para acceder a la memoria son también usadas para acceder a los

dispositivos. Para tener espacio para los dispositivos de E/S, las áreas del

espacio direccionable por la CPU deben ser reservadas para E/S más que para

memoria. Esta reserva puede ser temporal –Commodore 64 podía usar bank switch

entre dispositivos de E/S y memoria- o permanente. Cada dispositivo de E/S

monitoriza el bus de direcciones de la CPU y responde a cualquier acceso de

esta al espacio de direcciones del dispositivo, conectando el bus de datos con

la localización en memoria física del dispositivo deseado.

VENTAJAS

La ventaja de usar E/S mapeadas en memoria es,

dejando a un lado la complejidad extra que conlleva la E/S independiente, que

la CPU requiere menos lógica interna y es mas barata, rápida y fácil de

construir; esto sigue los principios básicos de RISC, y es también ventajoso en

sistemas embebidos. El hecho de que instrucciones regulares de memoria sean

usadas para direccionar dispositivos también significa que todos los modos de

direccionamiento de la CPU que están disponibles para E/S lo estén también para

memoria. Ya que los periféricos de 16 bits han quedado anticuados y han sido

sustituidos por los de 32 y 64 bits, reservar rangos del espacio de direcciones

para E/S no supone un gran problema.

REFERENCIAS BIBLIOGRAFICAS

Andrew S. Tanenbaum (2000), Organización de Computadoras un enfoque estructurado, Estado de México

John L. Hennessy y David A. Patterson (1993), Arquitectura de Computadoras un enfoque cuantitativo, Mcgraw-Hillpnteramericana De España

No hay comentarios:

Publicar un comentario