La

mayoría de las máquinas vectoriales permiten que los vectores sean tratados

como números en punto flotante (FP), como enteros, o como datos lógicos, aunque

nos centraremos en el punto flotante. La unidad escalar no es básicamente diferente

del tipo de CPU segmentada.

Hay

dos tipos principales de arquitecturas vectoriales: máquinas vectoriales con

registros y máquinas vectoriales memoria-memoria. En una máquina vectorial

con registros, todas las operaciones vectoriales -excepto las de carga y

almacenamiento- operan con vectores almacenados en los registros. Estas

máquinas son el equivalente vectorial de una arquitectura escalar de

carga/almacenamiento. Todas las máquinas vectoriales importantes construidas en

1990 utilizan una arquitectura vectorial con registros; éstas incluyen las

máquinas de Cray Research (CRAY-1, CRAY-2, X-MP e Y-MP), los supercomputadores

japoneses (NEC SX/2, Fujitsu VP200 y el Hitachi S820) y los

minisupercomputadores (Convex C- 1 y C-2). En una máquina vectorial

memoriamemoria todas las operaciones vectoriales son de memoria a memoria.

Las primeras máquinas vectoriales fueron de este tipo, como por ejemplo las

máquinas de CDC. A partir de este punto nos centraremos sólo en arquitecturas

vectoriales con registros; volveremos brevemente a las arquitecturas

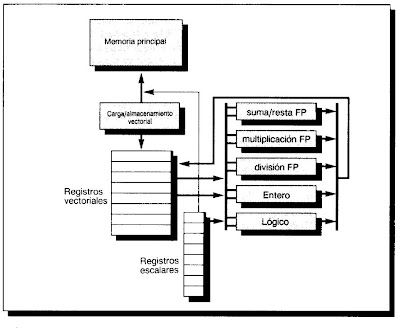

vectoriales memoria-memoria. Comenzamos con una máquina vectorial con registros

que consta de los componentes principales mostrados en la Figura 1.

Esta máquina, que está aproximadamente basada

en el CRAY- 1; la llamaremos DLXV; su parte entera es DLX, y su parte vectorial

es la extensión vectorial lógica de DLX.

Figura 1 Estructura básica de una arquitectura con registros vectoriales.

FUENTE: David

Patterson (2000)

Operaciones

Vectoriales

·

Todas

las operaciones vectoriales están segmentadas. En el DLXV, la suma tiene un

tiempo de inicio de 6 ciclos, y la multiplicación de 7. Las operaciones

aritméticas tienen latencia 1.

·

Las

cargas y almacenamientos en memoria también están segmentadas, con un tiempo de

inicio de 12 ciclos. Pueden realizarse operaciones en paralelo, siempre que

existan múltiples puertos de lectura y escritura en la memoria.

·

Grupo:

Conjunto de instrucciones vectoriales que pueden ejecutarse en paralelo. No

pueden tener ningún tipo de riesgo entre ellas.

·

Tiempo

de grupo: Tiempo aproximado de ejecución de una instrucción vectorial. Es

independiente del número de elementos del vector.

·

m

grupos con una longitud de vector

de n, tardarían m · n ciclos. Esto no es exacto, ya que falta el

tiempo de iniciación de las operaciones.

Ventajas de los procesadores

vectoriales:

Proporcionan

operaciones para trabajar con vectores. Una sola instrucción trabajo sobre

todos los elementos de un vector:

·

El

cálculo sobre los elementos de un vector suele ser independiente. Menos riesgos

de datos.

·

El

número de instrucciones es bajo. Se mitiga el cuello de botella de Flynn.

·

Los

accesos a memoria siguen un patrón fijo. Los elementos de los vectores están

ordenados.

·

Se

eliminan bucles y dependencia de control.

PROCESADORES

RISC

RISC se basaba en la idea de

que los procesadores eran más eficientes si las tareas que le eran entregadas

eran muy sencillas. Esto se reflejaba en gran parte al momento de

decodificar las instrucciones. Aunque el tener instrucciones más sencillas

implica un número más grande de las mismas, los procesadores tienden a ser más

eficientes al ejecutar este tipo de instrucciones que menos pero más complejas.

Algunas personas tienden a confundirse al pensar que

RISC significa un set de instrucciones más pequeño. Al contrario, las

instrucciones crecieron considerablemente, solo se hicieron más específicas en

lo que tenían que hacer, por ejemplo, existen instrucciones que se dedican

únicamente al acceso a memoria, pero por lo mismo, son más eficientes en lo que

hacen.

Esto también facilitó el desarrollo de lo que se

conoce como pipelines, que es dividir las tareas en instrucciones sencillas que

se puedan ir encolando para su ejecución “en paralelo”. Esto se dio en gran

parte a que se buscó que las instrucciones tardaran solo un ciclo de reloj para

ser ejecutadas (obviamente si era una búsqueda en memoria y los datos no

estaban disponibles, pues se perdía el propósito).

Características:

- Incrementar el tamaño del conjunto de registros.

- Mayor velocidad en la ejecución de instrucciones.

- Implementar medidas para aumentar el paralelismo

interno.

- Añadir cachés enormes.

- Añadir otras funcionalidades, como E/S y relojes

para minicontroladores.

- Construir los chips en líneas de producción

antiguas que de otra manera no serían utilizables.

- No ampliar las funcionalidades, y por lo tanto

ofrecer el chip para aplicaciones de bajo consumo de energía o de tamaño

limitado.

- Codificación uniforme de instrucciones (ejemplo:

el código de operación se encuentra siempre en la misma posición en cada

instrucción, la cual es siempre una palabra), lo que permite una

decodificación más rápida.

- Un conjunto de registros homogéneo, permitiendo

que cualquier registro sea utilizado en cualquier contexto y así

simplificar el diseño del compilador (aunque existen muchas formas de

separar los ficheros de registro de entero y

coma flotante).

- Modos de direccionamiento simple con modos más

complejos reemplazados por secuencias de instrucciones aritméticas

simples.

- Los tipos de datos soportados en el hardware (por ejemplo, algunas máquinas CISC tiene instrucciones para tratar con tipos byte, cadena) no se encuentran en una máquina RISC.

BIBLIOGRAFÍA

http://www.nebrija.es/~jmaestro/AT5118/Vectorial.pdf,

procesadores vectoriales, recuperado 21/04/2013

David Patterson (2000),

Arquitectura De Computadores Un Enfoque Cuantitativo, Madrid: España, editorial

Reverte

http://es.wikipedia.org/wiki/Reduced_instruction_set_computing,

Arquitectura Risc, recuperado 21/04/2013

http://quierobits.com/tecnologia/risc-explicando-la-arquitectura-de-los-procesadores/,

Explicación de la arquitectura Risc, recuperado 21/04/2013

No hay comentarios:

Publicar un comentario